数字电路基础 IC设计中的存储器件——从锁存器、触发器到寄存器

在集成电路(IC)设计中,存储器件是实现数据存储、状态保持与同步操作的核心组件,是构成复杂数字系统(如处理器、存储器阵列和通信模块)的基础。它们主要分为锁存器、触发器和寄存器三大类,虽然功能相似,但在工作原理、时序特性和应用场景上存在显著差异。理解这些器件是掌握数字系统设计的关键。

一、锁存器:电平敏感的存储单元

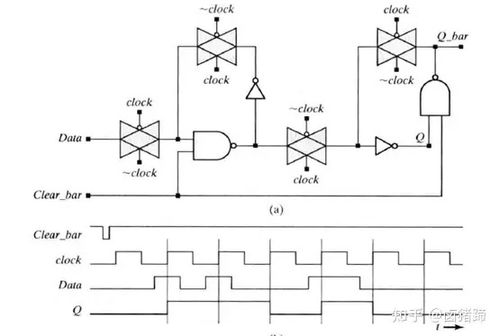

锁存器是基本的存储元件,其状态由控制信号的电平直接控制。最常见的类型是D锁存器。当使能信号(如时钟CLK或使能EN)为有效电平(通常为高电平)时,输出Q会实时跟随输入D的变化,相当于一个透明的“门”;当使能信号变为无效电平(如低电平)时,输出Q将锁定在使能信号跳变前一刻的输入值,并保持不变,从而实现数据存储。

锁存器的优点是结构简单,但存在“透明”特性,即在使能期间输入变化会直接传播到输出,易在时序电路中引发竞争冒险和亚稳态问题。因此,在现代同步IC设计中,锁存器通常用于特定场景,如数据锁存、总线保持,或作为更复杂触发器的一部分。

二、触发器:边沿触发的存储单元

触发器是同步数字电路中最常用的存储器件,其核心特点是状态变化仅发生在时钟信号的边沿(上升沿或下降沿),从而有效避免锁存器的透明性问题。最典型的代表是D触发器。

在时钟有效边沿到来时,触发器会采样该时刻的输入D值,并将其输出到Q,而在时钟的其他时刻,无论D如何变化,输出Q均保持不变。这种边沿触发机制确保了数据的稳定捕获和同步,大大增强了电路的可靠性和时序可控性。

触发器通常还包含异步控制端,如置位(SET,强制输出为1)和复位(RESET,强制输出为0),这些控制信号独立于时钟,用于初始化或强制状态。在IC设计中,触发器是构成时序逻辑(如状态机、计数器、流水线寄存器)的基本单元。

三、寄存器:多位触发器的集合

寄存器由一组(通常是多位,如8位、16位、32位)触发器并行构成,共享同一个时钟和控制信号,用于同时存储和操作一个数据字或指令。例如,一个8位寄存器包含8个D触发器,每个存储1位数据,共同构成一个8位存储单元。

寄存器在微处理器和数字系统中无处不在,用途包括:

- 数据暂存:如通用寄存器组,用于算术逻辑单元(ALU)的临时数据存储。

- 状态保持:如状态寄存器、控制寄存器。

- 接口缓冲:如输入/输出(I/O)寄存器。

寄存器设计需考虑多位数据的一致性、时钟偏移(skew)和功耗优化。

四、在集成电路设计中的考量

在IC设计流程(从RTL设计到物理实现)中,存储器件选择与优化至关重要:

- 时序收敛:需满足建立时间(Setup Time)和保持时间(Hold Time)的要求,确保数据在时钟边沿被正确采样。

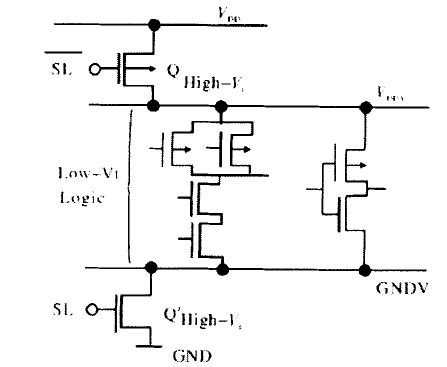

- 面积与功耗:触发器比锁存器结构复杂,通常占用更多面积和功耗。设计时需在性能、面积和功耗之间权衡,例如在高速路径使用触发器以保证稳定,在非关键路径可能使用锁存器以节省面积。

- 时钟树设计:寄存器的时钟信号需要通过精心设计的时钟树网络分发,以最小化时钟偏移和抖动。

- 可测性设计:通常通过扫描链技术将寄存器连接成链,以便在生产测试中注入和观测数据。

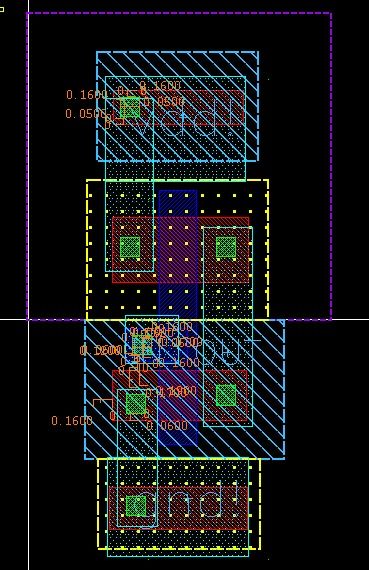

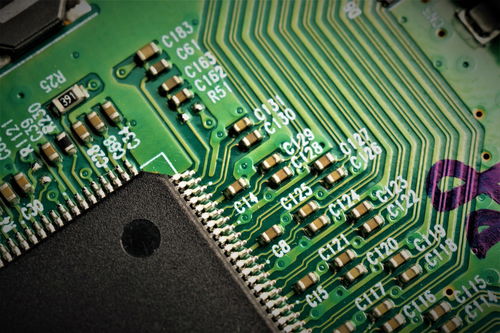

- 物理布局:存储单元通常作为标准单元库的一部分,布局需考虑连线长度、寄生效应和热分布。

###

从锁存器到触发器,再到寄存器,这些存储器件构成了数字IC存储层次的基石。锁存器的电平敏感特性适用于特定控制逻辑,触发器的边沿触发机制奠定了同步设计的主流范式,而寄存器则是数据通路与控制通路的实际载体。优秀的IC设计师必须深入理解它们的原理、特性与应用场景,方能在芯片设计中实现性能、面积与功耗的完美平衡,打造出高效可靠的集成电路系统。

如若转载,请注明出处:http://www.jisuyijian.com/product/51.html

更新时间:2026-01-13 09:59:39