基于集成电路CD4053的模拟开关型脉冲分解器设计

在集成电路设计领域,模拟开关型脉冲分解器是一种重要的信号处理模块,常用于数字系统中对脉冲信号进行分时、分路处理。本文详细阐述了基于模拟多路复用器/解复用器集成电路CD4053实现的模拟开关型脉冲分解器的设计原理、电路结构、工作过程及关键设计要点。

一、设计原理与核心器件

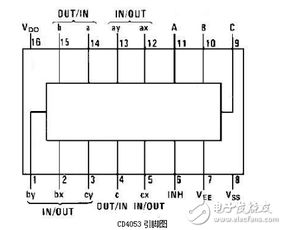

脉冲分解器的核心功能是将一路输入脉冲信号,根据控制逻辑,分配到多个输出通道中的某一个。CD4053是CMOS工艺制造的三通道二选一模拟多路复用器/解复用器。其内部包含三个独立的单刀双掷(SPDT)模拟开关,每个开关都能双向传输模拟或数字信号。通过控制引脚(A、B、C)的电平状态,可以精确选择每个开关的连通路径。这种特性使其非常适合构建一个基础的、低成本的多路脉冲分解器。其宽电源电压范围(3V至20V)和低静态功耗,增强了设计的灵活性和实用性。

二、电路结构设计

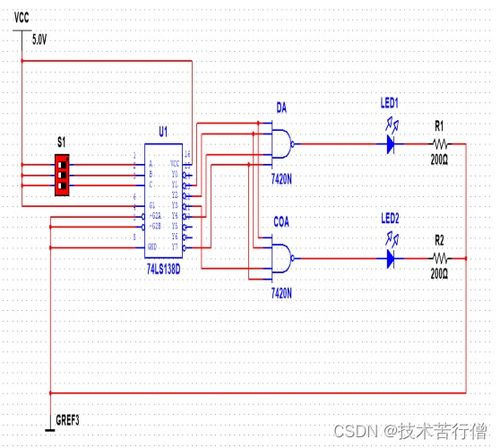

一个典型的基于CD4053的脉冲分解器电路结构如下:

- 信号输入部分:待分解的脉冲信号接入CD4053的公共输入/输出端(例如,三个开关的X公共端分别连接在一起作为总输入端)。

- 开关阵列:利用CD4053内部的三个开关。每个开关的两个独立通道(Y和Z)分别作为一个输出通道。这样,单个CD4053理论上可以提供最多6个(3开关×2通道/开关)输出通道的选择能力,但通常根据控制逻辑的简易性,设计为2-3个输出通道更为常见和直接。

- 控制逻辑部分:这是设计的核心。CD4053的通道选择由三个独立的二进制控制引脚A、B、C的电平决定。我们需要设计一个控制逻辑电路(例如,使用计数器、微控制器I/O口或简单的逻辑门电路),按照预定的时序或外部指令,生成特定的A、B、C编码,从而在特定时刻将输入脉冲引导至指定的输出通道。例如,可以设计一个两位二进制计数器,其输出Q1、Q0连接到CD4053的A、B引脚(C接地固定),这样每四个时钟周期,输入脉冲就会在四个可能的输出通道(对应开关1的Y、Z和开关2的Y、Z)间循环切换,实现一个简单的顺序脉冲分解器。

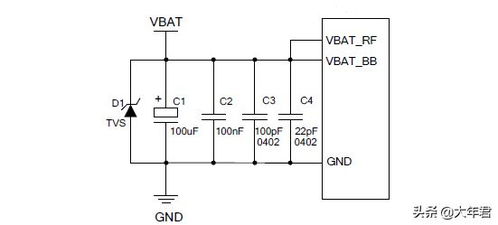

- 使能与电源:必须正确连接使能引脚(INH)。当INH为高电平时,所有开关断开。正常工作时,INH需接低电平。电源部分需注意为VDD提供正电源,VSS通常接地,VEE在单电源应用中接地,在需要处理负极性信号时可接负电源。

三、工作过程分析

假设设计一个将输入脉冲Pin分解到两个输出通道OUT1和OUT2的简单电路。我们可以使用CD4053中的一个开关,例如第一个开关(控制端A)。将Pin连接至该开关的公共端X,其Y通道连接OUT1,Z通道连接OUT2。控制端A的电平由外部逻辑提供:当A=0时,开关连通X与Y,脉冲从OUT1输出;当A=1时,开关连通X与Z,脉冲从OUT2输出。通过动态改变A端的逻辑电平,即可实现输入脉冲在两个输出通道间的动态分配。增加开关和控制线数量,即可扩展输出通道数。

四、关键设计要点与注意事项

- 信号完整性:CD4053作为模拟开关,其导通电阻(典型值125Ω)和关断漏电流会影响信号质量,尤其是在高频或高精度脉冲应用中。需评估其对脉冲边沿和幅度的影响,必要时可加入缓冲放大器进行整形和驱动。

- 开关速度与带宽:CD4053的开关速度有限(传输延迟时间在数十纳秒量级),限制了它能处理的最高脉冲频率。设计时需确保输入脉冲的宽度和周期远大于开关的切换与建立时间。

- 控制时序同步:控制信号(A、B、C)的切换时机必须与输入脉冲严格同步,避免在脉冲持续期间切换通道导致信号被切割或产生毛刺。通常要求控制信号在输入脉冲的无效期(如低电平期)完成变化并稳定。

- 电源去耦与布局:应在VDD和VSS引脚附近布置良好的高频去耦电容(如0.1μF),以减少电源噪声对开关性能的影响。PCB布局时,应尽量缩短信号路径,特别是高速脉冲走线,以减少分布电容和电感造成的信号失真。

- 电平兼容性:CD4053的控制逻辑电平以电源VDD和VSS为参考。若控制信号来自其他逻辑系列(如TTL),需注意电平匹配,确保在VDD=5V时,CD4053能可靠识别TTL的高、低电平。

五、

基于CD4053设计模拟开关型脉冲分解器,是一种结构简洁、成本低廉、易于实现的方案。它充分利用了集成电路内部集成的多个高精度模拟开关,通过外部数字逻辑进行灵活配置。尽管在超高速或超高精度场合存在局限性,但对于许多中低速数字系统、教学实验、仪器仪表通道切换等应用,该设计提供了可靠且高效的解决方案。设计师需要综合考虑信号特性、速度要求与控制逻辑的复杂性,进行合理的器件选型和电路优化,以确保脉冲分解的准确性和可靠性。

如若转载,请注明出处:http://www.jisuyijian.com/product/82.html

更新时间:2026-04-14 04:49:37